3月23日から25日にかけて鹿児島県天城町で開催された「第244回ARC・第202回SLDM・第62回EMB合同研究発表会(ETNET2023)」において、M2 の小森くんと M1 の本多くんが研究成果を発表しました。(小森くんの発表日は24日、本多くんの発表日は23日でした。)

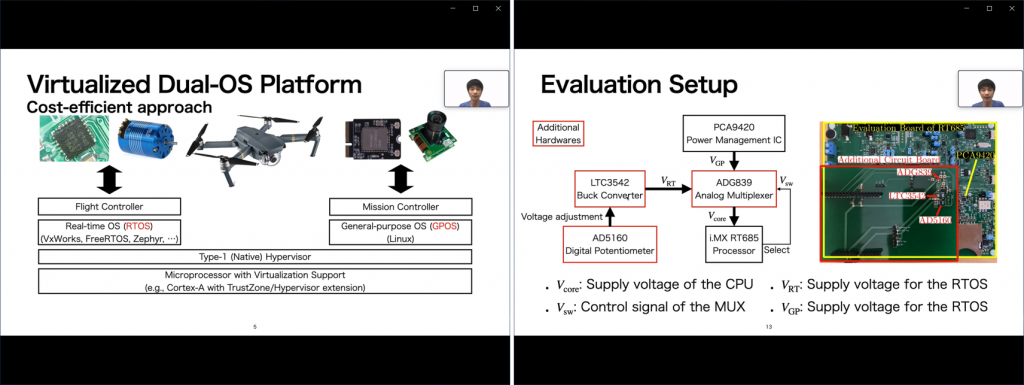

- 小森工,増田豊,石原亨, “RISC-V プロセッサにおける軽量デュアル OS 実行支援機構,” 第244回ARC・第202回SLDM・第62回EMB合同研究発表会 (ETNET2023), 天城町, 2023年3月.

- 本多 佑成,増田豊,石原亨, “近似計算の品質検証に向けたファジングのフィードバック調整手法の一検討 ,” 第244回ARC・第202回SLDM・第62回EMB合同研究発表会 (ETNET2023), 天城町, 2023年3月.