-

Domain Specific Processor Architecture

-

Energy Efficient Computing

-

In-Network Optical Computing

-

Quality-aware Adaptive Voltage Scaling

-

Verification of AC Design using Fuzzing

Domain Specific Processor Architecture

2016年以降、Google、Apple、Facebook、Amazon(いわゆるGAFA)やMicrosoftなどのICTサービス企業が、独自半導体チップの設計に乗り出したことは半導体業界で大きな話題となっています。国内でも、いくつかの自動車関連企業が独自のAI処理チップを開発しています。これらの企業が、他社から汎用チップを購入するのではなく、独自のチップを設計するのは、AI処理を高いエネルギー効率で実行することがICTサービスビジネスにとって大きな差別化要因になると考えたためだと思われます。

石原研究室では古くから、高いエネルギー効率を志向した独自のプロセッサアーキテクチャの研究を行っています。最近では、RISC-Vと呼ばれるプロセッサに基づいて、グラフ処理に特化した命令を追加したり、AI処理向けの近似演算アクセラレータを追加することによりプロセッサのエネルギー効率を最大化する方法を模索しています。世界中のICTサービス企業がそれまでの方針を転換して、独自の半導体チップを設計するようになる中、エネルギー効率の高いプロセッサアーキテクチャの研究は大学の研究室でも最重要研究課題となっています。

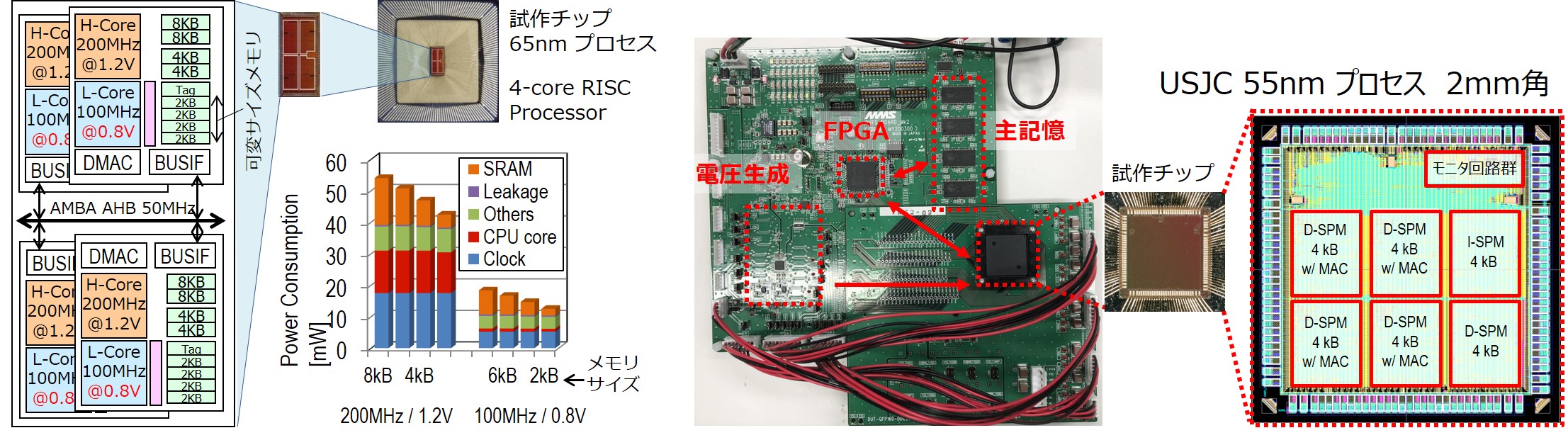

Energy Efficient Computing

エネルギー効率を最大化する計算の方法に関して、ハードウェア設計手法から計算アルゴリズムまで幅広く研究しています。

2018年10月からは、グラフ処理を高いエネルギー効率で高速化するプロセッサアーキテクチャに関する研究プロジェクトを開始しました。本プロジェクトは、東京大学および九州大学の研究グループと共同で実施しています。グラフ処理は、自動車やロボットなどの自動運転に欠かせない移動体自己位置推定や地図構築などに使われています。これらのグラフ処理を高いエネルギー効率で実現する方法を研究しています。具体的には、しきい値電圧近傍の非常に低い電圧で計算を実行するNear-Threshold Computingや、メモリの近傍でグラフ処理演算を実行するNear-Memory Computingの研究を実施しています。さらには、リアルタイムOSとの連携により、プロセッサ上で実行されるタスクに対して常に最適な動作電圧を使用させるための電圧スケジューリングの研究も推進しています。

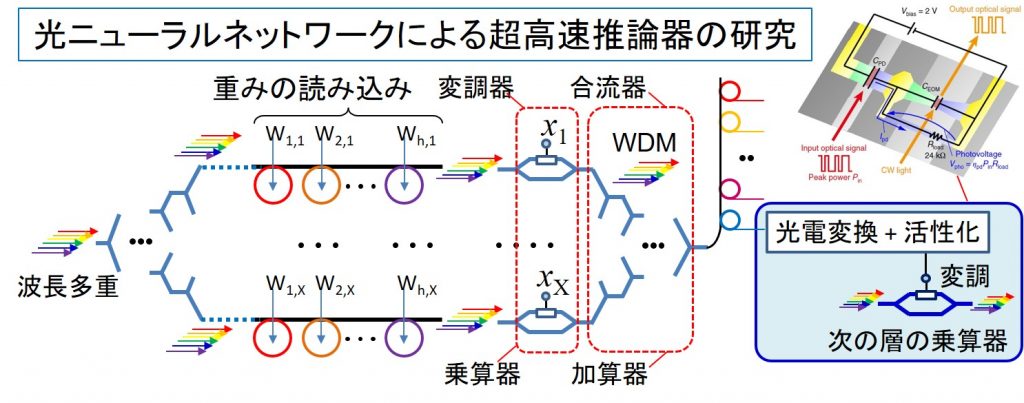

In-Network Optical Computing

光の通信ネットワーク中(In-Network)で簡単な計算を実行する方法を研究しています。光技術は従来、遠距離通信のための技術でしたが、近年のナノフォトニクス技術の急激な進展を背景に光技術が活躍する場所がどんどん近距離ネットワークにも拡大しつつあります。最近ではプロセッサチップ内のバス配線に光技術を適用する研究も活発に行われています。

石原研究室では、通信だけではなく光ネットワーク中の簡単な計算に光技術を利用(In-Network Computing)する研究を行っています。光の速度(100ミクロンの距離をおよそ1ピコ秒で伝搬)で信号を伝搬させることにより、従来のCMOS集積回路より一桁以上高速な光演算器を実現することを目指しています。特に、ニューラルネットワークなどの非ノイマン型コンピューティングを光によって高速化する研究を行っています。

本プロジェクトは、NTT、九州大学、京都大学と共同で実施しています。

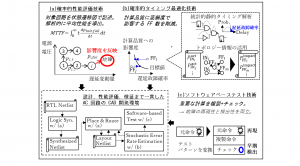

Quality-aware Adaptive Voltage Scaling

20世紀後半から21世紀初頭にかけて、集積システムは目覚ましい速度で、高性能化・省電力化・小面積化を推進してきました。この推進は、「トランジスタを小さく作る程、システムを多機能にでき、同時に消費電力と回路面積も削減できる」という指針 (ムーアの法則) に支えられてきました。一方、微細プロセスの開発コストの増大、トランジスタに対する物理的な制約の観点で、トランジスタの微細化には限界が訪れつつあります。

ポストムーア時代で省電力化・高性能化を推進するための設計パラダイムとして、近年、近似コンピューティング (AC: Approximate Computing) に注目が集まっています。これは、「重要な計算を正確に、他の計算を近似的に」行う指針で、機械学習、IoT、画像・音声・信号処理などの多分野での応用が期待されています。 AC 回路を実現するためには、回路設計から製造後テストまでの、幅広い設計開発支援技術 (CAD: Computer Aided Design) が必要不可欠です。私たちは、「計算の重要度」を定量的に取り入れた、新しい CAD 技術の開発を目指しています。

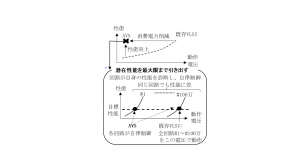

AC の回路設計では、目標の計算品質を考慮して、低消費電力化や高性能化を最大限高めることを目指します。一方、集積回路には、数10億個などの膨大な数のトランジスタ (回路を構成する基本パーツ) が搭載されていますが、実はこれらのトランジスタの性能は同一でなく、ばらつきがあります。従来の回路設計では、性能の最も悪い回路に動作速度を合わせており、他の大半の回路は自身の能力を十分に発揮することが困難でした。我々は、AC 設計パラダイムにより得られる効果 (高性能化・省電力化) を最大限高めるために、各回路が自身の潜在能力を 100% 引き出す設計パラダイムの実現を目指しています。

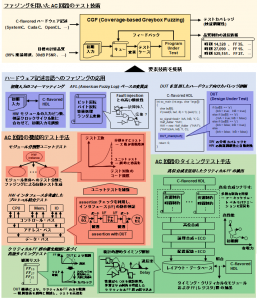

Verification of AC Design Using Fuzzing

AC 回路の検証では、どのようなテストパターンが、計算品質 (例. 機械学習の推論精度や画像処理のPSNR) を低下させるが検証する必要があります。しかし、従来の検証技術は「全てのパスが機能的・タイミング的に正しく動作すること」を前提として作りこまれており、AC 回路の機能的・タイミング的な近似特性の定量的取り扱いに課題がありました。

私達は、AC 回路の信頼性保証を目指して、「ファジング」を用いた検証技術の確立に取り組んでいます。ファジングは、ソフトウェアの不具合を発見するためのテスト手法であり、ソフトウェアのセキュリティに関する研究領域で盛んに研究されています。また、ファジングは、未知のバグや脆弱性を発見するだけでなく「ソフトウェアの品質」を定量的に評価する方法としても有望視されています。本研究では、このようなファジングの特性に着目し、ファジングを用いたAC 回路のテスト技術の開拓を目指しています。